LCD op MSX

Voor de echte

electronica liefhebber is de MSX nog altijd een grandioos systeem. De

cartridgeslots bieden enorm veel mogelijkheden voor elektronische toepassingen

zoals aansturen van audiomixer IC´s, ADC´s DAC´s noem maar op. Dit is één van

de redenen dat ik mijn MSX nog steeds zeer regelmatig gebruik. Vrijwel

maandelijks neem ik de MSX mee naar radiomarkten om daar besturingsprintjes

voor amateur-zenders te programmeren. Het probleem is dat er een monitor aan de

MSX vast zit, dat neemt niet zo makkelijk mee. Op een gegeven moment kwam ik op

het idee om er een laptop van te maken, de eerste stap is dan het LCD display.

In principe kan

je een standaard display op de MSX aansluiten en er een programma voor

schrijven, maar om het compatibel te houden is de enige oplossing om de VDP te

gebruiken. Het probleem hierbij is dat voor een LCD scherm digitale signalen

nodig zijn, en de VDP heeft alleen analoge uitgangen voor de intensiteit van

rood, groen en blauw. In grafische mode zou de colour-bus uitkomst bieden, deze

kan dan direct de digitale informatie van het beeld geven, maar in tekstmode is

deze onbruikbaar. De colour-bus is kennelijk puur de data uit het video

geheugen, dus sprites, pallet-kleuren en patronen van tekstmode worden in de VDP

gegenereerd en komen helaas niet uit de colour-bus... Dat betekend dat de

analoge uitgangen gebruikt moeten worden. Ik heb de TDA8706 gebruikt om deze om

te zetten naar digitaal, deze is redelijk goed verkrijgbaar maar er zijn andere

ADC´s.

De enige optie is

dan een LCD display van een (oude) laptop, er zijn diverse verschillende

soorten LCD display´s maar het principe van aansturing is over het algemeen

gelijk. Wie het principe van de TV kent (MSX principe dus), ziet direct een

grote overeenkomst. Zowel de TV als deze display´s geven één pixel weer, maar

omdat die ene pixel lijn voor lijn met een hoge snelheid van links naar rechts

beweegt, en de kleur op elke positie juist ingesteld wordt, wordt er een

plaatje gegenereerd.

Een LCD scherm

met een resolutie van 800 bij 600 heeft 600 lijnen en op elke lijn 800 punten.

De meeste LCD schermen hebben de volgende aansluitingen:

VS / VSync / SP VSync, hiermee geef je aan dat het

display naar de eerste (bovenste) lijn moet gaan.

DE / Dclk Dot-clock, in het ritme van dit signaal haalt

het display de pixels binnen en zet ze achter alkaar, van links naar rechts op

de lijn.

HS / HSync HSync,

hiermee geef je aan dat het display naar de volgende (onderligende) lijn moet.

DTMG / ENAB HSync, als het display naar een nieuwe lijn is gegaan

wacht het display met schrijven totdat dit signaal hoog wordt. Het display

triggert op een positieve flank, dus hoog

(Niet bij alle displays)

houden werkt helaas niet... Deze ingang kan in principe gewoon aan HSync gelegd

worden.

Proto type demonstrated at

Tilburg 2001, picture by Fony.

Het TFT scherm dat hier gebruikt is, is de LT121SS-105.pdf

Experiment

Op de MSX markt

in Tilburg in 2000 werden een aantal losse MSX2 moederborden gedumpt,

waarschijnlijk van een NMS8235, hiervan heb ik er een aantal gekocht om mee te

experimenteren. Helaas ontbreken er wel een paar onderdelen, er hoort nog een

klein printje bovenop voor het videosignaal, mijn monitor wou niet

synchroniseren maar verder doen die printen alles.

Globaal kunnen de

laptop schermen worden verdeeld over twee groepen, er zijn LCD schermen die uit

twee helften bestaan en er zijn LCD schermen die één geheel zijn.

De eerste groep

(DSTN) is voor de MSX niet echt bruikbaar. Deze display´s schrijven namelijk de

onderhelft en de bovenhelft tegelijk... Mijn eerste experiment was met een

LM64P80, dit is een zwart-wit display die ook uit twee helften bestaat. Ik wou

hier maar mee beginnen, het is een vrij oud display en als die in rook opgaat

is het minder erg dan een TFT scherm opblazen. Om het display goed te

doorgronden wou ik hem eerst aansluiten op de printerpoort van de PC zodat ik

de originele aansturing kon nabootsen, maar wat ik ook deed er kwam niets

zinnigs uit. Bij een bepaald datapatroon werd het beeld oranje (?) en trok hij

ineens een stroom van 1.5 Ampére i.p.v. 0.5 Ampére, na een minuut begon hij een

onaangename geur af te geven en heb ik hem maar weer eens uit gezet.

De originele

aansturing volgens de datasheet is eigenlijk niet goed te realiseren met de MSX

maar ik heb toch maar besloten om de MSX erop aan te sluiten. Een comparator

(LM339) zette het analoge signaal om naar een 1 bit digitaal signaal en uit het

CSync signaal kan je eenvoudig de VSync halen door middel van een RC filter.

Wat betreft de HSync, hiervoor kan direct het CSync signaal gebruikt worden

omdat de HSync van het LCD display triggert op de neergaande flank. En er was

beeld.

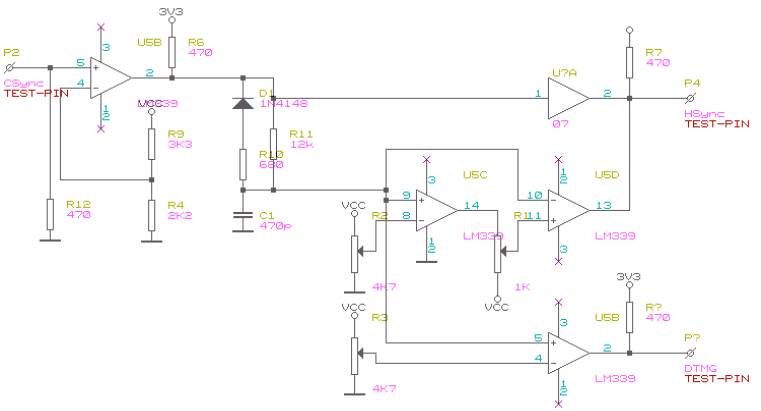

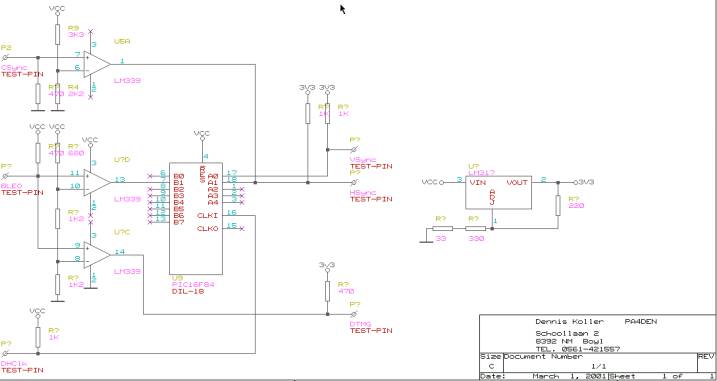

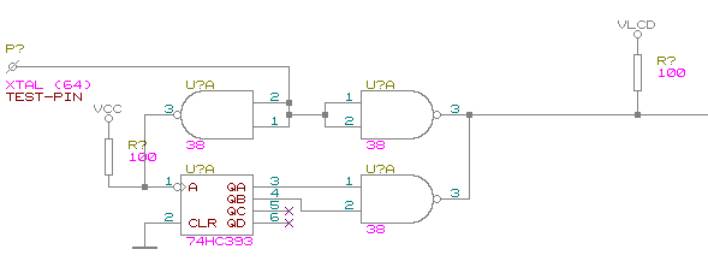

Schema

van de testopstelling

Bij een display

dat uit twee helften bestaat zijn de besturingssignalen hetzelfde, maar beide

helften hebben aparte data ingangen. De LM64P80 is 640*480, na een VSync begint

de bovenste helft op lijn 0 maar de onderste op 240. Dus bij een display dat

uit twee helften bestaat moet de data voor beide helften tegelijk beschikbaar

zijn... Dat is niet bij een MSX. Bij gebruik van zo´n display is het dus alleen

mogelijk om op één helft beeld te krijgen, of op beide helften hetzelfde beeld

door de datalijnen aan elkaar te leggen.

Uiteindelijk heb

ik toch heel voorzichtig, het kleuren scherm op de MSX aangesloten, met

dezelfde signalen. Dit scherm is van het type LT121SS-153 van Samsung, deze is

één geheel en heeft een resolutie van 800*600. Voor het gemak heb ik alle

datalijnen aan alkaar gesoldeerd en aan die fantastische 1 bit ADC gelegd en er

moesten nog wat buffers bijgeplaatst worden omdat het LCD scherm 3.3V is. Na

tien keer controleren heb ik hem maar eens aan gezet. En... helemaal niets!

Snel weer uit. Voor de Dot-clock had ik, voor de zekerheid, de 5MHz uitgang

(DLCLK) van de VDP gebruikt. Toen me de geur van het vorige weer te binnen

schoot, heb ik toch maar besloten om de DHCLK van 10MHz te gebruiken. En ja,

weer beeld! Het is kennelijk mogelijk om een LCD display te langzaam aan te

sturen...

In de datasheet

van het display staat eigenlijk officieel een minimale clock van 38MHz, maar

ja, dat kan niet. Bovendien staat voor elke puls beschreven hoeveel clockpulsen

of lijn-sync pulsen de puls actief moet zijn. Ook daar klopt niets van.

Gelukkig zit het display op een vrij logische, digitale manier in elkaar. Met

de datasheet hoef je het niet zo erg nauw te nemen, die is gebaseerd op

non-interlaced VGA signalen.

Interlacing

Toen werd het

eens tijd voor optimalisatie van de schakeling. Om het gehele beeld zichtbaar

te kunnen maken moet er rekening gehouden worden met de interlacing van de TV

standaard. Eerst worden alle oneven lijnen (dus lijn 1, dan lijn 3, dan lijn 5,

etc..) beschreven en daarna de even lijnen (2, 4, 6, etc..). Het onderscheid

tussen een even en een oneven raster kan bepaald worden d.m.v. de BLEO uigang

van de VDP of door het patroon van halve lijnen voor en na de VSync puls. De

laatste is de officiele methode, maar de MSX VDP geeft helaas bijna nooit een

echt interlaced signaal, in basic bijvoorbeeld niet. Met VDP register 9 ( VDP(10) ) kan interlace aangezet worden. Als de controle

uitgevoerd zou worden m.b.v. het aantal halve lijnen wordt er dus meestal maar

één raster op het LCD scherm beschreven. Daarom is het beter de BLEO uitgang te

controleren, deze wisselt altijd tussen even en oneven. Het nadeel is hiervan

is dat de schakeling alleen werkt op de V9938 en de V9958 en niet gebruikt kan

worden om bijvoorbeeld TV te kijken.

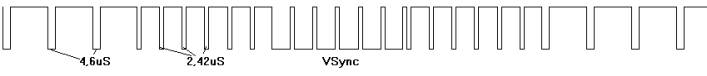

Bij elke HSync

moet het display dus twee lijnen verder gaan i.p.v. één, van lijn één naar lijn

3 of van lijn 2 naar lijn 4. Er moet dus telkens een lijn overgeslagen worden.

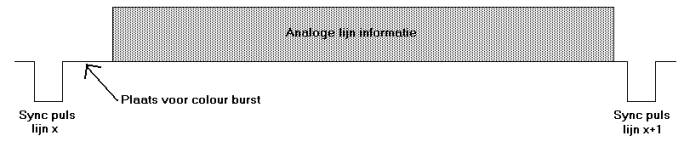

Dit is eenvoudig

op te lossen door een extra syncpuls te geven. De beste plaats voor deze extra

puls is ná de originele sync puls op de plaats van de colour-burst, dit is een

ruimte waar geen display data staat.

Origineel

signaal uit de VDP

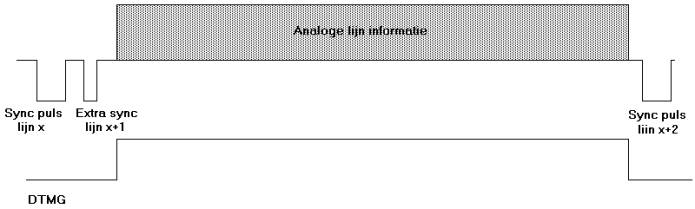

Om te voorkomen

dat het beeld gaat trillen moet in elk geval de DTMG puls telkens op een

constante tijd na de originele HSync van de VDP komen.

Signaal

voor het display

Dot clock

In mijn geval

wordt er een 800*600 display gebruikt, om het beeldvullend te krijgen moet er

een vrij hoge pixel-clock gebruikt worden. De totale schermbreedte is 512 plus

ca 16 punten voor de border. DHClk is

dus 10.738635MHz voor ca. 528 pixels, maar het scherm heeft 800 punten. Dus om

de data over de breedte uit te smeren moet 800 gedeeld worden door 528, dat is

1.51515. Dit getal vermenigvuldigen met de DHClk is 16.270659MHz. Het fraaiste

is dat dit signaal gerelateerd is aan de DHClk uitgang van de VDP. Wat er

gebeurt is het volgende:

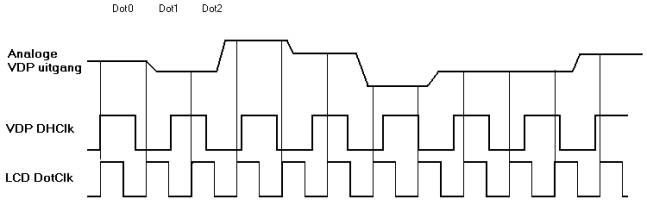

Als de

clocksignalen niet aan elkaar gerelateerd zijn worden de pixels die op de grens

zitten soms gelijk gemaakt aan de voorlopende en soms aan de volgende.

Bijvoorbeeld dot 1, in deze situatie is hij gelijk aan dot 0 maar als bij de

volgende lijn de DotClk net iets later is, wordt dot 1 gelijk aan dot 2. Dit

geeft nooit een perfect stilstaand beeld. Alle clocksignalen afkomstig van de

VDP staan direct in verband staan met het kristal. Dus het mooiste is om de

kristal frequentie te delen, maar dit zou betekenen dat de kristalfrequentie

gedeeld moet worden door door 1.32, dat is erg latsig. Het is mogelijk om te

delen door anderhalf door een oscillator van 42.9545 (2 * de kristalfrequentie)

te delen door 3, en de helft aan te bieden aan de VDP. Dit heeft tot gevolg dat

er een kleine strook aan de linker kant niet gebruikt wordt.

Voor kleinere

display´s is het makkelijkste om direct de DHClk te gebruiken, een display van

640*480 is dan op ca. 112 na pixels na voor het grootste deel gebruikt.

PIC

Controller

Om het aantal

analoge externe componenten te beperken, is het handigste om het meeste werk

door een PIC processor te laten doen. In een PIC zijn eenvoudig voorwaarden te

programmeren, bijvoorbeeld wanneer er nou wel of geen extra sync gegenereerd

moet worden.

In rust staat de

PIC in een loep van 2 instrukties te controleren of de CSync laag wordt, een

probleem hierbij is dat de tijd tussen de neergaande flank en het verlaten van

de loep niet constant is. De eerste instruktie is de controle zelf en kost

0,4uS en de tweede is een GOTO en kost 0,8uS. De neergaande flank kan op elk

moment komen, de PIC verlaat de loep dan ergens tussen de 0,4uS en 1,2uS na het

verschijnen van de neergaande flank. Voor de signalen HSync en VSync is een

speling van 0,8uS geen probleem, maar voor het DTMG signaal is dit teveel. Bij

een dot-clock van 16.27MHz komt 0,8uS overeen met 13 pixels.

Om ervoor te

zorgen dat het display op het juiste moment begint te schrijven wordt het BLEO

signaal van de VDP gebruikt. Het BLEO signaal geeft aan of er niets gebeurt, of

er een lijn van het even raster afgedrukt wordt, of een lijn van het oneven

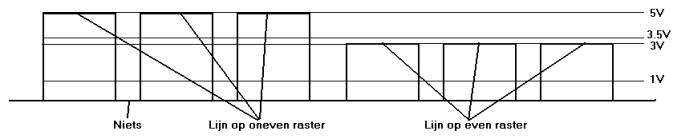

raster:

Deze uitgang kan

behalve 0 en 5 volt een tussenwaarde hebben van ongeveer 3 volt. Dit is dus net

niet digitaal, een comparator (LM339) maakt hier twee digitale signalen van, de

ene geeft aan dat BLEO > 1V en de andere geeft aan dat BLEO > 3.5V. Het

staat vast dat als BLEO > 1V, dat er een lijn geschreven moet worden, dit

signaal wordt gebruikt als DTMG signaal voor het display.

Schema

voor de synchronisatie

De PIC genereert

HSync en VSync uit het CSync signaal van de VDP en houdt daarbij rekening met

het even/oneven raster. Aan het digitale signaal uit de comparator voor BLEO

> 3.5V kan de PIC zien of het huidige raster even of oneven is.

PIC software

Het programma is

geschreven voor een clocksnelheid van 10MHz, de PIC kan dus geclockt worden

door de DHClk uitgang van de VDP.

Omdat de signalen

voor het LCD display 3.3 Volt zijn en de PIC 5 Volt uitgangen heeft, wordt er

softwarematig een soort open-collector uitgang gecreëerd. Dit wordt gedaan door

de uitgang vast in te stellen op laag (0V), en als er een hoog gegeven moet

worden wordt de uitgang als ingang geschakeld. De pull-up weerstanden trekken

het signaal dan naar de 3.3 Volt.

Voor een oneven

raster moet het display op lijn 1 beginnen en voor een even raster dus op lijn

2. Dat betekent dat er voor een oneven raster op de eerste lijn geen extra

sync-puls gegenereerd zou moeten worden. Een ander probleem hierbij is dat de

PIC na het detecteren van een HSync van de VDP dan eerst nog moet uitzoeken

wanneer er precies een extra sync gegeven moet worden. Omdat dit extra tijd

kost, ongeveer 4uS, duurt het 4uS langer voordat de extra sync gegeven wordt en

valt de extra sync in de beeld informatie en dan raken de eerste ca. 20 pixels

verloren. Daarom wordt er áltijd een extra syncpuls gegeven direct na de

originele, daarna kan de PIC nadenken en kan op één van de eerste lijnen

bovenaan nog een tweede exta syncpuls gegeven om op het even raster uit te

komen.

Aan het begin van

het programmais een kort stukje initialisatie geplaatst. Hier wacht de PIC ca.

70mS met het aanbieden van data aan het display, om ervoor te zorgen dat het

display goed opstart.

Bij het label

´MAIN´ staat de PIC te wachten tot het CSync signaal laag wordt. Als het laag

is en vrij direct weer hoog wordt, springt de PIC naar ´CHKH´. Duurt het wat

langer voordat het signaal weer hoog is, is de PIC inmiddels weer een paar

instrukties verder en springt hij naar ´HSYN´. Als het nóg langer duurt komt de

PIC vanzelf in de VSync routine. Per raster koaan het display, om ervoor te

zorgen dat het display goed opstart.aan het display, om ervoor te zorgen dat

het display goed opstart.mt de PIC 6* in dit VSync stukje, op de derde keer

wordt de VSync uitgang laag gemaakt en op de zesde keer weer hoog. Bij ´HSYN´

wordt eerst direct de extra HSync gegeven, daarna gecontroleerd of de 3e

HSync gegeven moet worden. De 3e sync wordt gegeven op de 12e

keer dat ´HSYN´uitgevoerd wordt én als BLEO>3.5V. Bij het detecteren van een

korte CSync puls wordt er verder niets gedaan, de PIC wacht tot het signaal

weer hoog wordt en begint opnieuw.

CSync

signaal uit de VDP

Kleuren

De eerste maand

heeft het LCD scherm eigenlijk geen fatsoenlijke kleuren weergegeven. Alle 6

datalijnen van rood, groen en blauw zaten aan elkaar dus elke kleur was

maximaal aan of uit. In totaal waren er acht kleuren zichtbaar, niet echt

ideaal. Het blijkt dat alle datalijnen geïnverteerd moeten worden, als alle

bits 0 zijn, is de kleur maximaal. In principe geeft het digitale getal op de

data-ingangen weer hoe sterk de kleur gedempt moet worden. Helaas is dit is nét

anders bij de VDP, een hogere spanning van de RGB uitgangen betekend een

heldere intensiteit op het scherm. Hoe hoger de spanning op het R pootje, des

te meer rood, hoe lager de spanning op G, deste minder groen etc. Vrijwel elke

AD converter geeft bij een lage spanning alle bits nul en bij een hoge spanning

één. Dit past dus niet helemaal, het LCD scherm geeft juist de maximale

intensiteit bij alle bits nul... Dit is op twee manieren op te lossen, óf alle

bitjes inverteren, óf het analoge signaal uit de VDP inverteren. Analoog

inverteren is mogelijk door een versterkertrapje met één transistor, maar dan

is het wel het beste om de versterker DC gekoppeld te houden en ook nog stabiel

bij temperatuurswisseling.

Het liep op een

gegeven moment vast op fatsoenlijke A/D converters, ik had gekozen voor het

type TDA8706A omdat mijn scherm 3,3V nodig had. Blijkbaar is het lastig om een

3,3V A/D converter te vinden, als er enigszins een keuze mogelijk is heeft 5V

duidelijk de voorkeur, 5V AD converters zijn er genoeg.

Op een gegeven

moment stond er op internet een adres waar de TDA8706 te krijgen was, die had

ik dus gekocht. Later bleek ook deze een 5V versie te zijn, jammer dan... Voor

3,3V moet het echt de TDA8706A zijn. Uiteindelijk heb ik toch deze ADC’s

gebruikt omdat het anders waarschijnlijk eindeloos gaat duren. Afgezien van de

spanningen op de data-uitgang is eigenlijk elke AD converter te gebruiken die

tot ca 16MHz kan omzetten, voor de TDA8706 kan bijvoorbeeld ook een TDA8703

genomen worden. Een andere veel voorkomende AD converter is de TDA8708, deze

heeft meer mogelijkheden maar die zijn eigenlijk totaal overbodig... Al deze

mogelijkheden worden verder niet gebruikt, bovendien heeft hij meer externe

componenten nodig en heeft hij een grotere behuizing. Het voordeel is dat hij

wel beter te krijgen is. Deze AD converters zijn oorspronkelijk ook bedoeld

voor video signalen, ze hebben dus in elk geval een ‘Clamp’ ingang.

Omdat voor deze

5V AD converter toch een extra buffering nodig is naar de 3V3 voor het display,

wordt hier het inverteren gedaan m.b.v. een inverterende buffer. In dit geval

zijn er ook geen analoge problemen.

Naast het analoge

signaal van de VDP heeft de AD converter nog een clock en een clamp signaal

nodig.

Clock:

Elke keer bij het

hoog worden van het clocksignaal zet de AD converter het analoge signaal om en

wordt de digitale data op de uitgangen gezet. In principe zou deze clock met de

DHCLK van de VDP gestuurd kunnen worden, omdat de VDP met DHCLK aangeeft of er

een nieuwe pixel geschreven wordt. De analoge uitgang van de VDP veranderd dus

ook hoogstens één keer per DHCLK periode, en bij een resolutie van 256 zelfs

één keer per twee DHCLK periodes. Één keer per DHCLK het analoge signaal

omzetten zou voldoende zijn, maar een voorwaarde is dat dan ook het LCD scherm

dezelfde clock krijgt. Als het LCD scherm een clocksignaal krijgt wat niet in

verband staat met de clock van de AD converter, ontstaat er een soort sneeuw in

beeld. Dit wordt veroorzaakt doordat de AD converter bij elke clock puls even

tijd nodig heeft om de nieuwe omgezette data goed op de data-uitgangen te

zetten. Het omzetten van een data-uitgang van 0 naar 5V of terug kost altijd

even tijd. Het LCD scherm kijkt eveneens in het ritme van de clock naar zijn

data-ingangen, als de clock van de AD converter en het LCD scherm niet

synchroon lopen zal het geregeld voorkomen dat het scherm de data leest terwijl

de databits nog niet goed staan, valse data dus...

Een lastig

probleem is dat een heleboel TFT-LCD schermen geen lagere clock dan 14MHz

bijken te accepteren, dit is een groot probleem voor LCD schermen van 640*480.

De VDP geeft 512 pixels in het ritme van DHCLK, de DHCLK is 10.738MHz dus elke pixel

duurt 1 / 10.738Mhz = 93.12ns. Alle 512 pixels op een rij duren dus 512 *

93.12ns = 47,67us. Als het LCD scherm van 640 pixels een clock van 14MHz

krijgt, doet hij er 45.7us over om alle 640 pixels te beschrijven, de VDP heeft

dan nog 2uS te gaan en alle pixels in de laatste 2uS vallen dus buiten het

scherm... Een LCD scherm van 800*600 doet er bij 14MHz ongeveer 57,1uS over,

bij schermen van 800*600 en hoger raakt er dus geen beeld-informatie verloren.

Clamp:

Bij een zwart

scherm worden de analoge uitgangen van de VDP ongeveer 2,6V en bij volledig wit

3.6V. Het bereik van de AD converter ligt tussen 2,2V en 3,1V. Met een

spanningsdeler is dit goed te benaderen. Het clamp signaal wordt gebruikt om

ervoor te zorgen dat de AD converter bij het zwart nivo ook constant een

digitale 0 geeft. De AD converter moet weten en onthouden welk analoog

spanningsnivo voor zwart staat. De VDP geeft tussen de HSync en het begin van

de lijn-informatie een korte tijd een zwart nivo, in deze periode valt bij het

PAL systeem de colour-burst voor het synchroniseren van de kleurdecodering in

PAL ontvangers. Deze zwart-periode wordt gebruikt om de ADC’s op in te stellen,

de PIC processor volgt het videosignaal en weet wanneer het zwart nivo komt, op

dit moment geeft de PIC een puls op uitgang B6.

Naast de Clamp

uitgang heeft de PIC nog een extra functie gekregen. LCD schermen moeten

gedurende een aantal miliseconden geen data krijgen na een power-up. Het blijkt

dat in sommige gevallen het LCD scherm last krijgt van latch-up, in dit geval

wordt scherm onduidelijk. Eens verkeerd opgestart blijft verkeerd, totdat de

spanning van het display af wordt gehaald. Om dit te voorkomen houdt de PIC de

ingangen van het display laag bij het opstarten, dit is makkelijk te doen omdat

alle gebruikte drivers open-collector drivers zijn i.v.m. de conversie naar

3,3V.

Optimalisatie

Door het gebruik

van een los-staande 16MHz oscillator, bleef het beeld altijd nog een beetje

onrustig. Het enige wat hier tegen te doen is, is de clock synchroniseren met

de clock van de VDP of de clock ervan afleiden. Het handigste is waarschijnlijk

om de kristalfrequentie van de VDP te

gebruiken, dit is de klok vaaruit de VDP al zijn signalen afleidt, maar dit is

tevens de hoogste frequentie die aanwezig is. Het is makkelijker om een

frequentie te delen dan te vermenigvuldigen. De kristalfrequentie is 21.477MHz,

om op ongeveer 16MHz uit te komen moet deze frequentiedus gedeeld worden door

1,5. het is niet het makkelijkste deeltal maar het is goed te doen. Dit is een

schema waarmee in dit geval de clock gedeeld wordt door 1,5:

Clock divider, 21.47727 *

3/4

De NAND poorten

zijn weer een open drain versie om voor het display op 3v3 uit te komen. De

74HC393 is een standaard een binaire teller, deze telt mee met het clock signaal,

bij elke clock-puls komt de volgende binaire waarde op de uitgang. Eerst zijn

de A en B uitgangen beide 0, één clock puls later wordt uitgang A hoog, nog één

clock puls later wordt B hoog en A laag, weer één clock puls later worden beide

uitgangen hoog. De C en D uitgangen tellen op dezelfde weize door maar zijn

niet van belang. Het gaat erom dat de NAND poort die aan uitgangen A en B zit,

de clock blokkeerd als A en B beide hoog zijn. In deze situatie wordt namelijk

de uitgang van deze NAND laag en houdt dus d.m.v. het wired-and principe de

clock uitgang van de andere NAND laag. In principe zijn er dus twee uitgangen

aan elkaar gekoppeld, dit kan geen kwaad omdat beide uitgangen alleen naar de

0V kunnen schakelen, er kan dus nooit de situatie optreden dat de ene driver

+5V op de clock wil zetten en de andere 0V. Op deze clock uitgang wordt ook nog

een uitgang van de PIC aangesloten, om het LCD scherm goed op te starten bij

het inschakelen. De PIC is softwraematig zó geschakeld dat deze pin een uitgang

is die een 0 stuurt, óf een ingang is als er een 1 (mag) komen.

Verder hadden de

aan elkaar bebakte componenten het probleem dat de verbindingsdraden te lang

waren geworden. Als een frequentie van 16MHz door een open-collector poort

gaat, moet er al een behoorlijk lage pull-up weerstand op om nog een redelijke

blok zichtbaar te maken. Bij 3v3 is de maximale pull-up weerstand ongeveer

100Ohm. Nadat alles redelijk ‘netjes’ op een experimenteerprintje was gezet was

het beeld al weer zichbaar stabieler. Tot slot was er een hoop verbetering te

winnen door meer te ontkoppelen. Bij CMOS IC’s die op 16MHz draaien en ook nog

een voedingsdraad hebben van 10cm is met de scoop een rimpel van 1V op 3,3v te

meten... Bij elke overgang van laag naar hoog of andersom trekken IC’s

stroompulsen die door de inductie van dat draadje een spanningsval geven van 1V

over dat draadje. Dit betekend dat de voeding soms 2.3v is en dan weer 3.3v,

dit is niet zo erg gunstig voor een stabiel beeld... Dit probleem is opgelost

m.b.v. véél ontkoppel condensatoren, voor elke voeding bij elk IC één

condensator van 100nF. Dit is ook gebruikelijk maar tijdens het testen heb ik

nooit zin gehad om ze erop te solderen, achteraf was het beter om het direct te

doen omdat het een stuk makkelijker experimenteerd.

Het programma is

aangepast voor Clamp signaal voor de ADC’s en voor de opstart-vertraging:

; VSync

generator met even/odd delay

; A0 = U

VSYNC

; A1 = HSYNC

; B1 =

I BLEO

; B6 =

U Clamp

; B7 =

U Mute clock

; VSYNC counter 0D

; HSYNC

counter 0F

; Wait

loop 14

list p=16f84

#include

p16f84.inc

BSF 03,5

MOVLW 07F ;Port B pull-up

MOVWF 01

MOVLW 0FC ;Iint port A, VSync and HSync are

held low when pin in output mode

MOVWF 05

MOVLW 03F ;Init port B, ADC clamp and

LCDclock are held low when pin in output mode

MOVWF 06

BCF 03,5

MOVLW 0FC ;Set pins to output mode

MOVWF 05

MOVLW 000

MOVWF 06 ;Now all outputs are held

low

CLRF 0D ;Reset VSync counter

MOVLW 3 :Wait to prevent latch-up

MOVWF 15

CLRF 14

CLRF 13

INIT: DECFSZ 13,1

GOTO INIT

DECFSZ 14,1

GOTO INIT

DECFSZ 15,1

GOTO INIT

BSF 03,5 ;Release the inputs

BSF 05,0 ;Set VSync pin to input mode

BSF 05,1 ;Set HSync pin to input mode

BSF 06,7 ;Set LCDclock pin to input

mode

BCF 03,5

MAIN: BTFSC 05,1 ;Read CSync input

GOTO MAIN ;Still high à wait

BSF 06,6 ;Let ADC clamp the DC level, when

sync is low…

BTFSC 05,1

GOTO CHKH

BTFSC 05,1

GOTO CHKH

BTFSC 05,1

GOTO CHKH

BTFSC 05,1

GOTO CHKH ;High already à short sync pulse means

line contains no picture information, jump to CHKH

BTFSC 05,1

GOTO HSYN

BTFSC 05,1

GOTO HSYN

BTFSC 05,1

GOTO HSYN ;Longer sync pulse, jump to HSYN

;----------------------------------------------------------

VSync pulse -------------------------------------------------------------

MOVLW 0F3 ;Reset

HSync counter

MOVWF 0F

INCF 0D,1 ;Vertraging VSync

MOVFW 0D

SUBLW 003

BTFSS 03,2 ;3e

keer?

GOTO VSY1

BSF 03,5

;Ja, VSync laag

BCF 05,0

BCF 03,5

VSY1: MOVFW 0D

SUBLW 006 ;Lengte

VSync puls

BTFSS 03,2 ;6e

keer?

GOTO CHKH

BSF 03,5

;Ja, VSync hoog

BSF 05,0

BCF 03,5

GOTO CHKH

;----------------------------------------------------------

HSync pulse -------------------------------------------------------------

HSYN: BCF 06,6 ;A longer sync pulse means the

line contains picture information

BSF 03,5 ;Switch CSync pin to output to

generate the extra sync pulse

BCF 05,1

NOP

NOP

NOP

NOP

BSF 05,1

BCF 03,5

CLRF 0D ;Reset VSync counter

MOVLW 008 ;Wait for BLEO

MOVWF 14

WAIT: DECFSZ 14,1

GOTO WAIT

BTFSS 0F,7 ;Time

to give third sync pulse?

GOTO CHKH ;Already done this frame, jump to

CHKH

INCF 0F,1 ;Increase line counter

BTFSS 03,2

GOTO CHKH ;Not

yet

BTFSC 06,1 ;Time for third sync, is this

even frame?

GOTO CHKH ;No, odd frame à no

third sync

BSF 03,5 ;Give third sync pulse

BCF 05,1

NOP

NOP

NOP

NOP

BSF 05,1

BCF 03,5

NOP ;Wait

to prevent unvalid pulse detection due to capacitance of CSync line

NOP

NOP

NOP

CHKH: BCF 06,6 ;Disable ADC clamping

CHKW: BTFSS 05,1 ;End of CSync pulse?

GOTO CHKW

GOTO MAIN ;Yes, jump to MAIN again

dw

0x0102

dw

0x0304

dw

_LP_OSC & _PWRTE_OFF & _WDT_OFF & _CP_OFF

end

Het

uiteindelijke schema